# SWISS\*PHOTONICS

# Scalable electro-optical packaging of silicon photonics components

#### **Bert Jan Offrein**

Swissphotonics workshop Miniaturized Photonic Packaging

#### Outline

- The need for integration at component and system level

- CMOS silicon photonics with embedded III-V materials

- High channel count silicon photonics packaging

- Summary

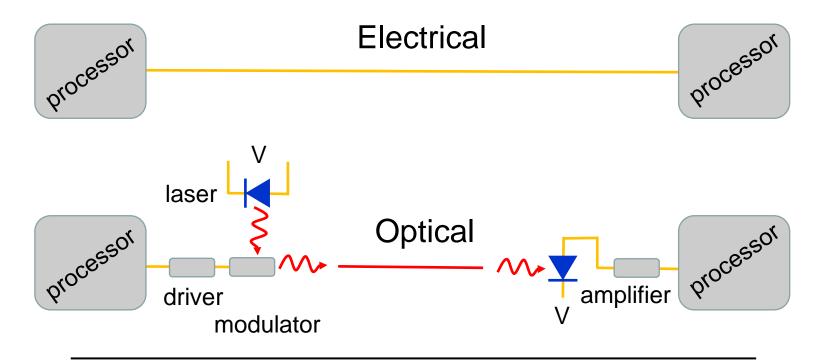

#### Communication between two processors

- 1000 x Larger bandwidth

- Optical communication:

- 1000 x Lower loss

- 100 x Larger distance

- Scalability & Power efficiency !!!

Optical communication requires many more components and assembly steps !!!

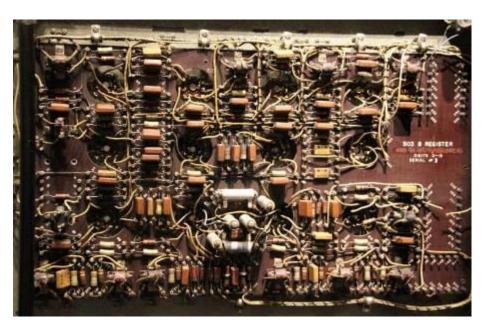

#### Why integration? Looking back, electronics

#### Whirlwind, MIT, 1952

EAI 580 patch panel, Electronic Associates, 1968

#### Today's state of computing is based on:

- Integration and scaling of the logic functions (CMOS electronics)

- Integration and scaling of the interconnects (PCB technology & assembly)

#### For optical interconnects, this resembles:

- Electro-optical integration and scaling of transceiver technology

- Integration of optical <u>connectivity</u> and signal <u>distribution</u>

# Photonics technologies for system-level integration

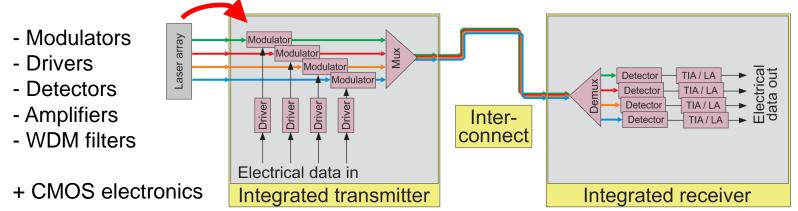

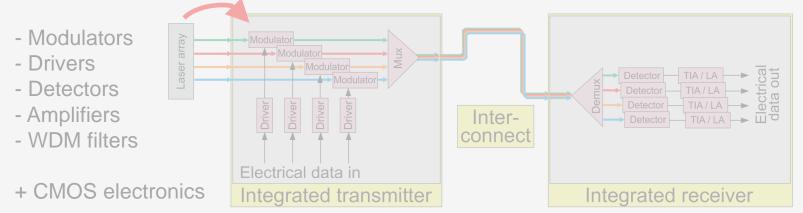

#### **1** <u>Chip-level</u>: CMOS silicon photonics + Active photonics devices

Si photonics provides all required buliding blocks (except lasers) on chip-level:

#### 2) <u>System-level</u>: Scalable chip-to-fiber connectivity

- One step mating of numerous optical interfaces

- Provide electrical and optical signal routing capability

- Enable a simultaneous interfacing of electrical and optical connections

# Photonics technologies for system-level integration

#### **1** <u>Chip-level</u>: CMOS silicon photonics + Active photonics devices

Si photonics provides all required buliding blocks (except lasers) on chip-level:

2) <u>System-level</u>: Scalable chip-to-fiber connectivity

- One step mating of numerous optical interfaces

- Provide electrical and optical signal routing capability

- Enable a simultaneous interfacing of electrical and optical connections

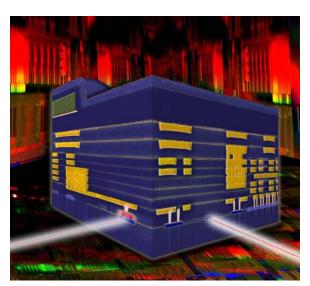

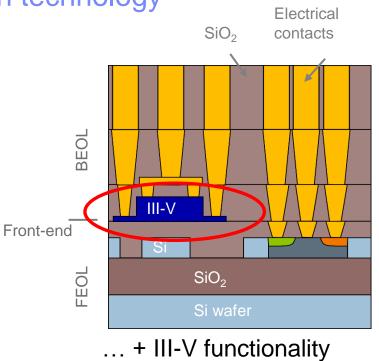

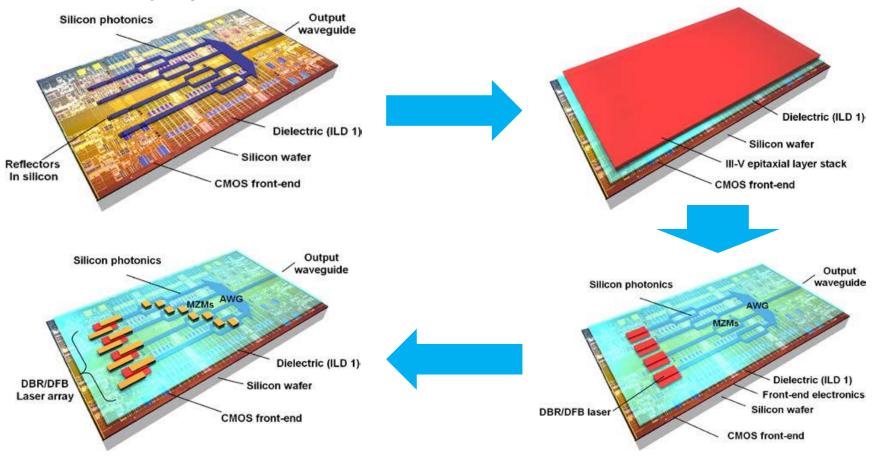

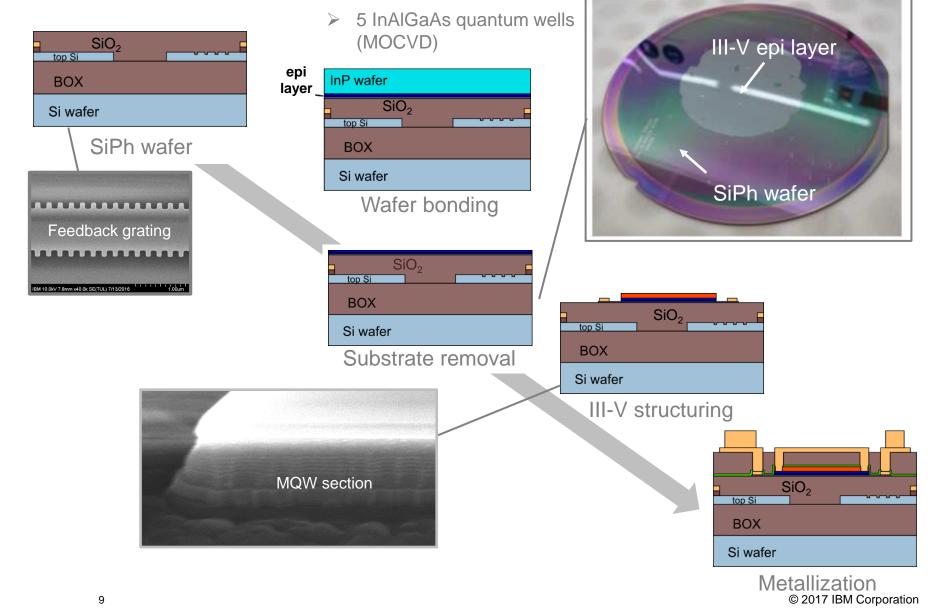

#### CMOS Embedded III-V on silicon technology

**CMOS Si Photonics**

- Overcome discrete laser and assembly cost

- New functions, tightly combining electronics, passive and active photonics

#### H2020 EU project DIMENSION

#### **Processing scheme**

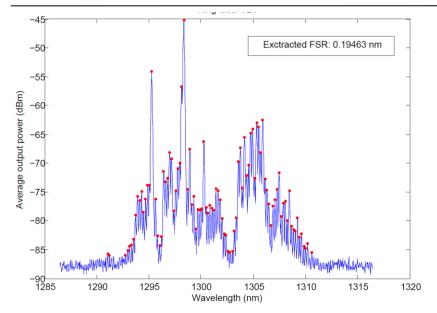

#### Optically pumped ring laser

Measured FSR: 0.194 nm

Estimated FSR from ring: 0.203 nm Estimated FSR from III-V: 0.266 nm

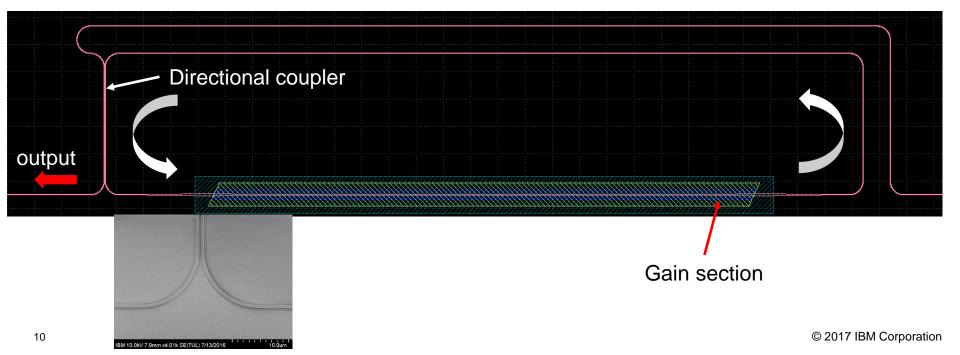

#### Lasing with feedback from silicon photonics

# Photonics technologies for system-level integration

#### 1) <u>Chip-level</u>: CMOS silicon photonics + Active photonics devices

Si photonics provides all required buliding blocks (except lasers) on chip-level:

#### 2) <u>System-level</u>: Scalable chip-to-fiber connectivity

- One step mating of numerous optical interfaces

- Provide electrical and optical signal routing capability

- Enable a simultaneous interfacing of electrical and optical connections

IBM

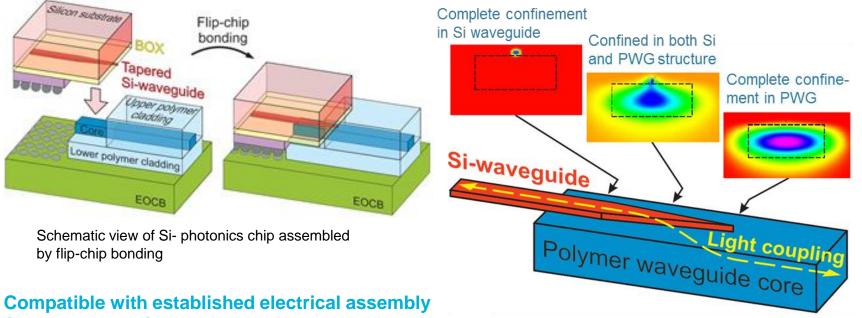

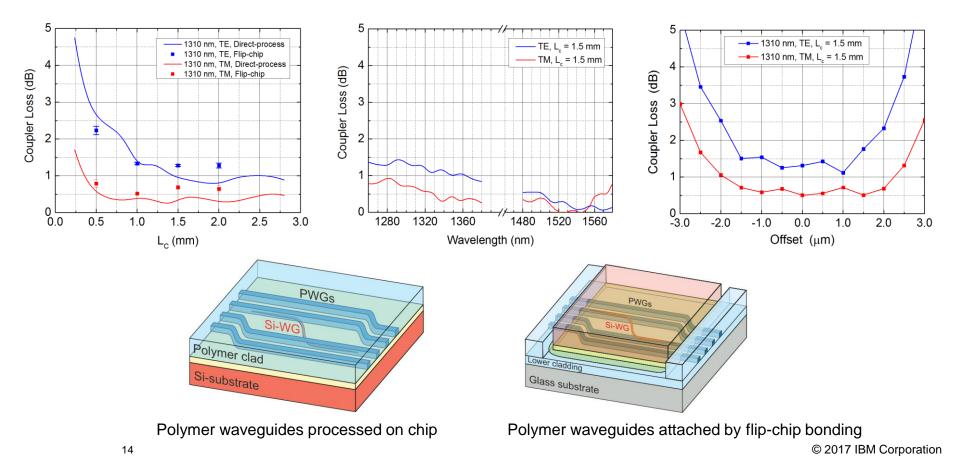

#### Adiabatic optical coupling using polymer waveguides

#### **Principle:**

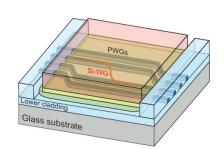

Contact between the silicon waveguide taper and the polymer waveguide (PWG), achieved by flip-chip bonding, enables adiabatic optical coupling

- Simultaneous E/O interfacing

- Scalable to many optical channels

- J. Shu, et al. "Efficient coupler between chip-level and board-level optical waveguides." Optics letters 36.18 (2011): 3614-3616.

- I. M. Soganci, et al. "Flip-chip optical couplers with scalable I/O count for silicon photonics." Optics express 21.13 (2013): 16075-16085.

- T. Barwicz, et al. "Low-cost interfacing of fibers to nanophotonic waveguides: design for fabrication and assembly tolerances.", *Photonics Journal, IEEE* 6.4 (2014): 1-18.

•

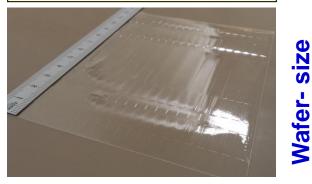

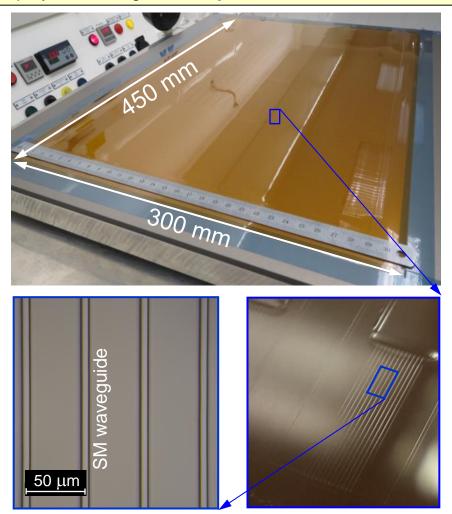

### Single-mode polymer waveguide technology

# chips (e.g. Si photonics chips)

SM polymer waveguides on

SM polymer waveguides on wafer-size flexible substrates

R. Dangel, et al. Optics Express, 2015

SM polymer waveguides on **panel-size flexible** substrates

Panel-size

#### Adiabatic coupler loss characterization

#### Coupler loss measurement:

- Direct-process vs Flip-chip bonding approach

- For  $L_c \ge 1.0$  mm: Coupler loss < 1.5 dB, PDL  $\le 0.7$  dB

- Operating in the O and C-band

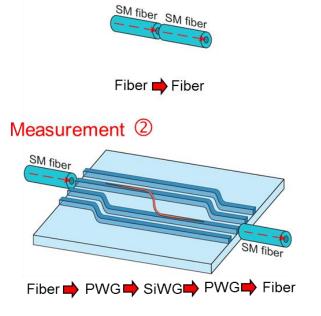

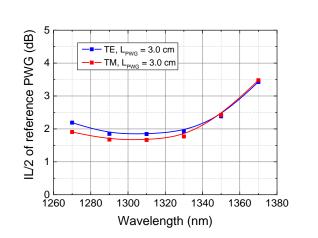

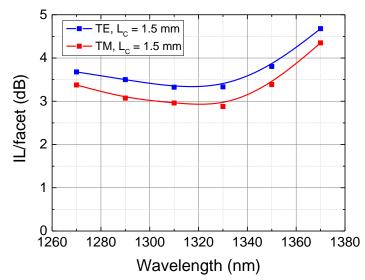

#### Insertion loss characterization (1)

#### Insertion loss measurement:

- Wavelength sweep over O-band

- Full path vs ref. PWG path

- Wavelength dependency mainly in the PWG

Measurement ①

#### **Insertion loss per 2 facets**

Schematic view of Siphotonics chip assembled by flip-chip bonding

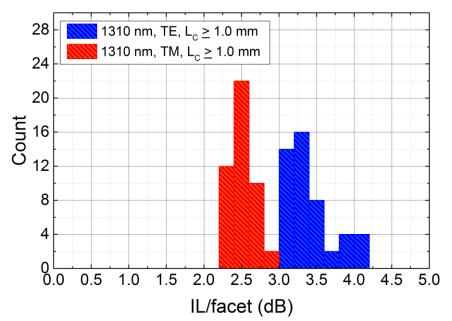

#### Insertion loss characterization (2)

#### Insertion loss statistics:

- High number of optical interfaces: **152** per chip

- 94 interfaces for silicon couplers

- 58 interfaces for polymer waveguide references

- For  $L_C = 0.5$ , 1.0 mm, ..., 3.0 mm

| Polymer waveguides                 | PWG Chip           |               | 1 |

|------------------------------------|--------------------|---------------|---|

| Polymer waveguides   Si waveguides |                    | SiWG Chip     |   |

| Polymer waveguides                 |                    | •             |   |

| Polymer waveguides                 |                    | •             |   |

| Polymer waveguides                 |                    | •             |   |

|                                    | Polymer waveguides | Si waveguides |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

| •                                  |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

| :                                  |                    | •             |   |

| •                                  |                    |               |   |

| •                                  |                    | Ŧ             |   |

|                                    |                    | •             |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

|                                    |                    |               |   |

Top-view of Si-photonics chip assembled by flip-chip bonding

~100 functional assembled optical IO's per chip

- 94 optical interfaces per chip, assembled simultaneously

- 17 connections used for offset measurements (34 interfaces)

- 30 connections for coupler length variations (60 interfaces)

- 24 (48 interfaces) from 25 connections plotted above, only one connection not functional

#### Acknowledgements

- Collaborators in IBM

- Marc Seifried, Herwig Hahn, Gustavo Villares, Lukas Czornomaz, Folkert Horst, Daniele Caimi, Charles Caer, Yannick Baumgartner Daniel Jubin, Norbert Meier, Roger Dangel, Antonio La Porta, Jonas Weiss, Jean Fompeyrine, Ute Drechsler

- And many others

- Co-funded by the European Union Horizon 2020 Programme and the Swiss National Secretariat for Education, Research and Innovation (SERI)

- The opinion expressed and arguments employed herein do not necessarily reflect the official views of the Swiss Government.

Agreement No 688003

Agreement No 688172

Agreement No 688544

Agreement No 688572

Contract No 15.0313

Contract No 15.0339

Contract No 15.0346

Contract No 15.0309

18

#### Summary

#### Miniaturized Photonic Packaging

- Chip level integration

- CMOS+Passive+Active photonics

- System-level integration

- Adiabatic optical coupling as a scalable, efficient, broadband and polarization independent fiber-to-chip interfacing solution

#### Thank you for your attention

- Bert Jan Offrein

- ofb@zurich.ibm.com